Возникают ситуации, когда сигнал поступает в ПЛК с задержкой. Для необходимо задержать поступление сигнала на вычисление. Такая коррекция так же может быть применена для моделирования динамических свойств объекта [1].

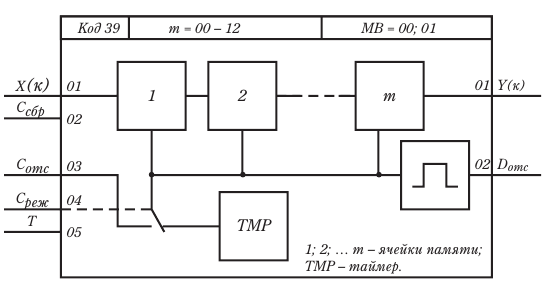

Если обратиться к программному обеспечению, то можно отметить что в кросс-средстве Редитор для контроллера Ремиконт Р-130 имеется подобный алгоритм. Это алгоритм ЗАП (рисунок 1) [1].

Рисунок 1 – Функциональная схема алгоритма «Запаздывание ЗАП».

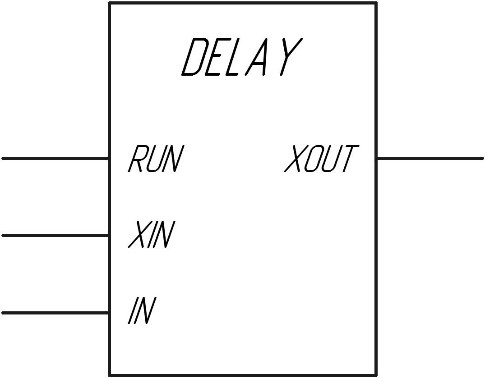

При этом стандартом программирования промышленных контроллеров МЭК 61131-3 также предусматривается реализация алгоритма цифровой задержки (рисунок 2) [2]. В таблице 1 представлен перечень входов и выходов функционального блока «DELAY» из стандарта МЭК 61131-3.

Рисунок 2 – Функциональный блок цифровой задержки в стандарте МЭК 61131-3.

Таблица 1 – Входы и выходы алгоритма «DELAY» стандарта МЭК 61131-3.

|

Назначение |

Входы/выходы |

Тип переменной |

|

| Входы |

Запуск алгоритма |

RUN |

BOOL |

|

Основной вход |

XIN |

REAL |

|

|

Значение задержки |

IN |

DWORD |

|

| Выход | Основной выход |

XOUT |

REAL |

Если обратиться к современным средам автоматизации, таким как Codesys [3], Step 7 [4, 5], PC Worx [6], TwinCat [7], то данный алгоритм отсутствует в стандартных библиотеках перечисленных средств программирования.

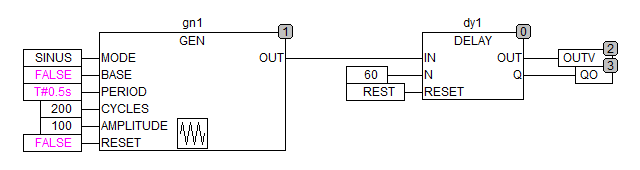

В данной статье предлагается рассмотреть возможность применения алгоритма цифровой задержки из пользовательской библиотеки упомянутой в статьях [8, 9, 10]. В качестве среды разработки для него было выбрана программная среда Codesys, поскольку среди перечисленных имеет широкий круг программируемых ПЛК. На рисунке 3 представлен внешний вид функционального блока «DELAY» на графических языках FBD / CFC. В таблице 2 представлены значения входных и выходных переменных функционального блока «DELAY».

Рисунок 3 – Внешний вид функционального блока «DELAY»для пользовательской библиотеки.

Таблица 2 – Входы и выходы алгоритма «DELAY».

| Назначение | Входы/выходы | Тип переменной | |

| Входы | Основной вход | IN | REAL |

| Значение задержки | N | INT | |

| Сброс работы алгоритма | RESET | BOOL | |

| Выход | Основной выход | OUT | REAL |

| Сигнал о работе алгоритма | Q | BOOL |

На рисунке 4 представлена реализация алгоритма цифровой задержки на языке ST.

Рисунок 4. Реализация алгоритма «DELAY» на языке ST.

При этом если на вход N, отвечающий за количество циклов задержки подано нулевое значение, или на вход RESET, отвечающий за сброс работы алгоритма подана значение TRUE, алгоритм не работает, о чем сигнализирует выход Q, принимающий значение FALSE, и на выход OUT подаётся вход IN. В противном случае Q принимает значение TRUE, а входная переменная буферизируется во временной переменной BUF. Далее организован цикл с накоплением переменной i. При этом выходной переменной OUT присваивается значение буфера BUF, что организует задержку.

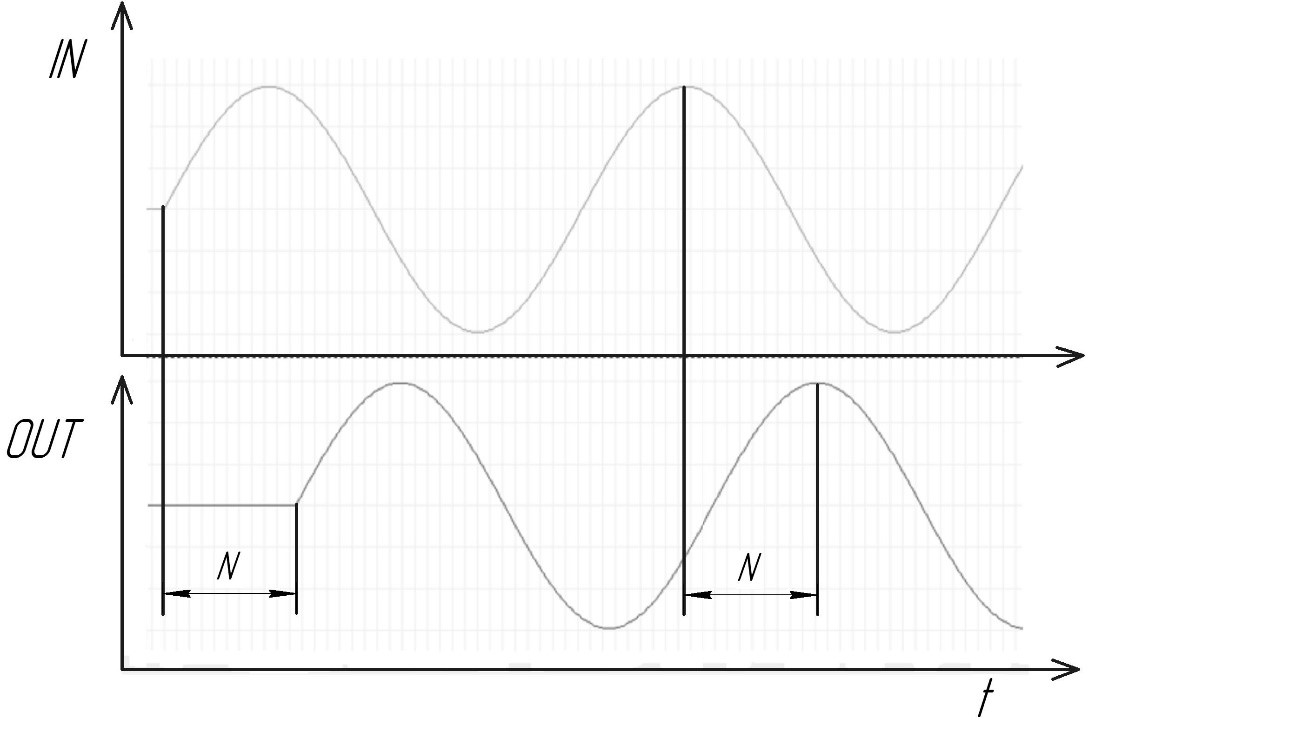

Проверка работоспособности алгоритма «цифровой задержки DELAY» была проведена в среде Codesys в режиме эмуляции, а также при использовании контроллера ОВЕН ПЛК-150.У-М. Для этого была использована программа, представленная на рисунке 5, в результате работы программы была получена диаграмма, изображенная на рисунке 6.

Рисунок 5. Программа для проверки алгоритма «DELAY».

Рисунок 6. Демонстрация работы алгоритма «DELAY».

На рисунке 6 изображена трассировка переменных с помощью, встроенной в среду Codesys возможности. Входной сигнал IN представляет собой синусоиду, подаваемый с генератора, Выходной сигнал OUT имеет задержку от входного сигнала на N циклов. В данном случае задержка N равна 60 циклам, в контроллере Овен ПЛК-150.У-М было установлено значение цикла в 2мс, это значит, что задержка функции происходила на 30 мс. Это значение можно выставить в диапазоне от 1 до 4095 циклов. Это значение – размер буфера памяти BUF и оно может быть отрегулировано в соответствии с нуждами пользователя.

Разработанный алгоритм имеет широкие возможности в области применения в различных программах. Помимо этого, данный алгоритм может быть использован в процессе обучения и исследования возможностей современных программных комплексов.

Библиографический список

- Микропроцессорный контроллер Ремиконт Р – 130. – М.: НИИТЕПЛОПРИБОР, 1990. – 330с.

- Karl-Heinz John, Michael Tiegelkamp., IEC 61131-3: Programming Industrial Automation Systems. – Springer, 2001г – 376 p.

- Руководство пользователя по программированию ПЛК в CoDeSys 2.3 [Электронный ресурс]: Режим доступа: http://www.kipshop.ru/CoDeSys/steps/codesys_v23_ru.pdf

- Hans Berger., Automating with STEP 7 in LAD and FBD, 2008 – 440p.

- Hans Berger., Automating with STEP 7 in STL and SCL, 2012 – 553p.

- User Manual UM QS EN PC WORX EXPRESS [Электронный ресурс]: Режим досступа: http://select.phoenixcontact.com/phoenix/dwld/um_qs_en_pc_worx_express_7632_en_02.pdf?cp=y&asid2=7541554902303

- Beckhoff New Automation Technology TwinCAT 2 [Электронный ресурс]: Manual. Режим доступа: ftp://ftp.beckhoffautomation.com/TwinCAT_Manual/TwinCAT%202%20Manual%20v3.0.1.pdf

- Севастьянов Б.Г., Жолобов И.А. Алгоритм таймера пользовательской библиотеки [Электронный ресурс] / Севастьянов Б.Г., Жолобов И.А. // Инженерный вестник Дона: электрон. науч. журнал. - 2013. - № 4. - C. Режим доступа: http://www.ivdon.ru/magazine/archive/n4y2013/2207.

- Севастьянов Б. Г., Жолобов И. А., Севастьянов Д. Б. Принципы программирования контроллеров на языке FBD [Электронный ресурс] / Севастьянов Б.Г., Жолобов И.А., Севастьянов Д.Б. // Инженерный вестник Дона: электрон. науч. журнал. - 2014. - № 2. - C. Режим доступа: http://www.ivdon.ru/magazine/archive/n2y2014/2344.

- Жолобов И.А., Казакова Л.Г., Корзин В.В. Программная реализация вычислительного блока струйной системы измерения температуры потока газа [Электронный ресурс] / Жолобов И.А., Казакова Л.Г., Корзин В.В. // Инженерный вестник Дона: электрон. науч. журнал. - 2014. - № 2. - C. Режим доступа: http://www.ivdon.ru/magazine/archive/n2y2014/2329.