Программируемые логические интегральные схемы (ПЛИС), в том числе FPGA (Field-Programmable Gate Array) позволяют реализовывать различные схемные решения, выступая в роли специализируемого под конкретную задачу сопроцессора или автономного вычислителя. Причём современные платы позволяют переключаться со схемы на схему «на лету».

При этом создание схемных решений для этих сопроцессоров часто представляет серьезную проблему. Для прикладного программиста или научного работника эта проблема связана зачастую с необходимостью обладать специальными знаниями в области схемотехники, а иногда – и в области схемотехники конкретных устройств FPGA. Даже для специалистов-схемотехников задача разработки специализированного решения может потребовать значительных затрат времени.

Использование специальных языков описания аппаратуры (HDL), прежде всего VHDL и Verilog, конечно, позволяет несколько сократить время разработки по сравнению с разработкой схем в графическом редакторе САПР ПЛИС, но, по сути, не снимает проблемы ориентации средств разработки в основном на схемотехников. И по-прежнему время даже прототипирования решений сложных вычислительных задач остается значительным.

Для преодоления этих препятствий разработаны и разрабатываются ряд высокоуровневых средств, позволяющих генерировать непосредственно прошивку FPGA (байт-код) или описание на VHDL или Verilog из исходного кода на языке программирования высокого уровня.

В данной статье рассмотрены некоторые средства высокоуровневого проектирования для FPGA.

Веб-компилятор C-to-Verilog работает с программами, написанными на языке C, накладывая на них ряд ограничений: требуется отсутствие рекурсивных функций, указателей на функции, структур и вызовов библиотечных функций (printf, malloc и других), операций с плавающей запятой. При использовании нескольких функций их необходимо объявлять как static inline. Поддерживаются только одномерные массивы. Использовать в функции можно только те массивы, которые были переданы в качестве параметров функции. [1]

C-to-Verilog производит оптимизацию с помощью распараллеливания и конвейеризации. Кроме того, возможна оптимизация под архитектуру нескольких модельных рядов FPGA от Xilinx и Altera. Разработчики позволяют использовать их компилятор и локально, однако это возможно только на платформах Linux.

Кроме того, C-to-Verilog также генерирует и модуль тестирования, предназначенный для моделирования системы в средствах отладки.

Надо заметить, что при задании некоторых параметров генерации полученный код не компилируется средой моделирования из-за наличия ошибок. Также необходимо обратить внимание на некоторые особенности создаваемых модулей. Во-первых, данные из входной памяти должны выдаваться сразу же после подачи в неё адреса, что трудно реализуемо при работе с реальной памятью. Если же данные из памяти выдаются на следующем такте, результаты работы не соответствуют требуемым. В связи с этим адаптация схемы для использования в реальной системе затруднена. Второй особенностью является задержка между выдачей значений, которая составляет несколько тактов, что трудно объяснимо в простейших случаях.

Средство высокоуровневой разработки, выпущенное университетом Торонто, – проект LegUp ([5]) – предоставляет возможность как полностью перевести исходную программу в логическую схему, так и разделить операции между аппаратной частью и процессором, размещаемым на кристалле FPGA. В текущей версии LegUp разработчик должен вручную выбрать функции, которые необходимо разместить в FPGA, однако в дальнейшем планируется делать это автоматически по результатам профилирования.

LegUp так же, как и предыдущие проекты, накладывает ряд ограничений на базовый язык, главным из которых является отсутствие поддержки операций с плавающей запятой. Кроме того, компилятор проекта работает только под управлением операционной системы Linux.

Тестирование компилятора показало что описание интерфейса, данное в руководстве LegUp, по крайней мере в исследованных случаях не соответствует генерируемому модулю, поэтому удостовериться в корректности результатов работы этих модулей не удалось.

Коммерческий проект Impulse CoDeveloper предполагает реализацию алгоритма на специальном языке ImpulseC, который представляет собой C с некоторыми ограничениями (запрет на использование рекурсии, сильно ограниченный набор поддерживаемых функций и структур) и дополнениями (специальные типы данных и функции). Кроме того, Impulse CoDeveloper имеет специальную среду разработки, которая позволяет создавать проекты по шаблонам и осуществлять отладку программы в режиме симуляции аппаратной схемы. [3]

Impulse CoDeveloper предполагает реализацию программных и аппаратных процессов, связанных коммуникационными объектами (потоками данных, разделяемой памятью, сигналами, регистрами, семафорами). Программные процессы выполняются на размещённом на чипе FPGA процессоре, аппаратные реализуются схемами.

Интерфейсы генерируемых Impulse CoDeveloper модулей подробно описаны. Кроме того, возможно создание модулей с интерфейсами, поддерживаемыми ведущими производителями FPGA – компаниями Altera и Xilinx.

Коммерческий продукт Mitrion Platform ([4]) предполагает следующие шаги разработки приложения: реализовать вычислительно сложные функции на MitrionC, выполнить вызовы этих функций в основной программе специальными вызовами Mitrion Platform API, отладить с помощью Mitrion SDK приложение, сгенерировать конфигурационные файлы для FPGA.

MitrionC расширяет стандартный C с помощью собственных объявлений типов, списков, векторов и потоков, конструкций циклов и функций. При этом длина программы ограничена объёмом программируемой логики, за адресацию памяти в FPGA отвечает пользователь, отсутствуют исключения (деление на ноль, выход за пределы массива).

Mitrion Platform API предоставляет следующие возможности: резервирование FPGA для приложения, загрузка логической схемы, запуск и остановка выполнения, пересылка данных между платой и системной памятью, а также наблюдение за выполнением алгоритма.

Серьёзным недостатком Mitrion Platform является поддержка ограниченного круга платформ FPGA.

С лета 2008 года ведётся разработка стандарта межплатформенного параллельного языка программирования OpenCL. Цель разработки – перенос параллельных алгоритмов с платформы на платформу с минимальными затратами. В основу OpenCL положен язык C с добавлением специфических для параллельных программ расширений.

OpenCL предполагает построение приложения из двух блоков. Хост-часть выполняется на микропроцессоре (CPU или встроенном в FPGA) – это обычная программа на стандартном C/C++. Вычислительно сложные части приложения предлагается располагать во втором блоке – так называемых ядрах – которые и будут выполняться на ускорителе (стандарт подразумевает возможность использования и GPU, и FPGA). Для написания ядер используется всё тот же C, но со специальными расширениями для использования параллелизма ускорителя. Для связи двух частей приложения используется OpenCL API – набор функций для хост-части, позволяющий обмениваться данными с ускорителем, а также запускать ядра на выполнение. Один из ведущих мировых производителей FPGA – компания Altera – уже опубликовала первые обнадёживающие результаты использования собственного компилятора, поддерживающего стандарт OpenCL, однако он пока не доступен для широкой аудитории. [2]

Отечественный проект Автокод-HDL представляет сильно отличающуюся от рассмотренных выше проектов концепцию. Авторы проекта пришли к выводу о непригодности традиционных языков программирования, ориентированных на архитектуру фон Неймана. Они разрабатывают новый язык высокоуровневого проектирования логических схем для реконфигурируемых устройств – Автокод-HDL – который объединяет в себе краткость языков высокого уровня и ориентированность на доступную в FPGA аппаратную архитектуру (схемотехническую модель программирования). [6]

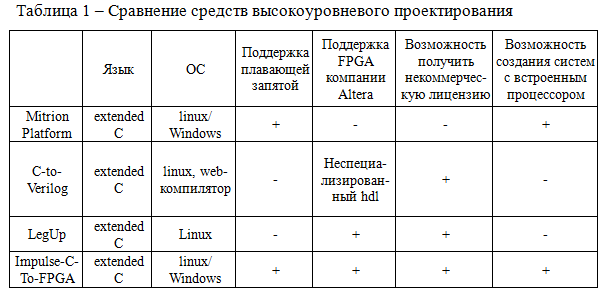

Краткие результаты сравнения средств высокоуровневого программирования приведены в таблице 1.

В результате проведенного сравнения средств разработки авторами были отобраны для дальнейшего рассмотрения два перспективных некоммерческих проекта средств высокого уровня: LegUp и Автокод-HDL, а также ознакомительная версия коммерческого средства Impulse-C. В настоящее время проводится их изучение и реализация с помощью этих средств ряда алгоритмов (криптографических, базовых ортогональных преобразований, итерационных численных методов).

Список использованной литературы:

1. Rotem, N. C-to-Verilog FAQ [Электронный ресурс] / Nadav Rotem. – 2009. – Режим доступа : http://www.c-to-verilog.com/faq.html

2. Implementing FPGA Design with the OpenCL Standard [Электронный ресурс] / Altera Corporation. – 2011. – Режим доступа : http://www.altera.com/literature/wp/wp-01173-opencl.pdf

3. Impulse Tutorial: Generating HDL from C-Language [Электронный ресурс] / Impulse Accelerated Technologies, Inc. – 2009. – Режим доступа : http://www.impulseaccelerated.com/Tutorials/Basic/Tutorial_Basic_HW_Gen.pdf

4. Mitrion Users’ Guide [Электронный ресурс] / Mitrionics AB. – 2008. – Режим доступа : http://forum.mitrionics.com/uploads/Mitrion_Users_Guide.pdf

5. LegUp: High-Level Synthesis for FPGA-Based Processor/Accelerator Systems [Электронный ресурс] / A. Canis [и др.] // University of Toronto, Altera Toronto. — 2011. — Режим доступа: http://legup.eecg.utoronto.ca/fpga60-legup.pdf

6. Технологии разработки прикладного ПО для реконфигурируемых вычислительных структур [Электронный ресурс] / С.С. Андреев [и др.]. – 2010. – Режим доступа : http://sdat.ispras.ru/archive/2010/20100318_Latsis.pdf